Finite State Machine Verilog takes middle stage, this opening passage beckons readers right into a world crafted with good data, guaranteeing a studying expertise that’s each absorbing and distinctly unique. With the arrival of complicated programs and software program design, Finite State Machines (FSMs) in Verilog have turn into important parts in embedded programs and digital electronics. This text will take you on a journey by the basics of Finite State Machines in Verilog, from idea and kinds to designing and implementing them.

The idea of a finite state machine, often known as an automaton, was first launched within the Nineteen Forties by the American mathematician and pc scientist Samuel Finett. A finite state machine is a mathematical mannequin that consists of a set of states, a set of inputs, and a set of outputs. It’s used to explain the conduct of a system or a tool by way of its inputs and outputs.

Fundamentals of Finite State Machine (FSM) in Verilog

A Finite State Machine (FSM) is a mannequin of computation that can be utilized to design digital circuits, significantly sequential circuits. It makes use of a set of states to explain the conduct of the circuit in response to inputs. In Verilog, an FSM is described utilizing a set of registers to retailer the present state and a set of combinational logic to find out the following state and output.

Kinds of Finite State Machines in Verilog

FSMs will be broadly categorised into two sorts: Moore and Mealy machines.

- Moore Machine: Any such FSM makes use of the present state itself to find out the output. The output doesn’t depend upon the enter or the following state. The Moore machine will be carried out utilizing a combinational logic circuit and a set of registers.

- Mealy Machine: Any such FSM makes use of the present state and the enter to find out the output. The output is determined by the enter, present state, and subsequent state. The Mealy machine may also be carried out utilizing a combinational logic circuit and a set of registers.

Each Moore and Mealy machines will be carried out in Verilog utilizing an identical syntax.

Moore Machine Implementation in Verilog

Here is an instance of a easy Moore machine carried out in Verilog:

“`verilog

module moore_machine(enter reset, enter clk, enter[1:0] x, output[1:0] y);

reg [1:0] state;

reg [2:0] y;

all the time @(posedge clk)

if (reset)

state <= 0;

else

case (state)

0: state <= x[1] ? 1 : 0;

1: y <= x[0] ? 2 : 1;

endcase

endmodule

```

Mealy Machine Implementation in Verilog

Here is an instance of a easy Mealy machine carried out in Verilog:

“`verilog

module mealy_machine(enter reset, enter clk, enter[1:0] x, output[1:0] y);

reg [1:0] state;

reg [2:0] y;

all the time @(posedge clk)

if (reset)

state <= 0;

else

case (state)

0: state <= x[1] ? 0 : 1;

0: y <= x[0] ? 2 : 1;

1: state <= x[1] ? 2 : 1;

endcase

endmodule

```

On this instance, the Mealy machine makes use of a single state and two doable outputs. The output is decided primarily based on the present state and enter.

Variations between Mealy and Moore Machines

Some key variations between Mealy and Moore machines embody:

- In Moore machines, the output is decided by the present state, whereas in Mealy machines, the output is decided by the present state and enter.

- Moore machines have an easier combinational logic circuit in comparison with Mealy machines, which have a extra complicated combinational logic circuit.

- Moore machines are extra appropriate for digital circuits that require deterministic conduct, whereas Mealy machines are extra appropriate for digital circuits that require asynchronous conduct.

In abstract, Moore and Mealy machines are each forms of FSMs that can be utilized to design digital circuits in Verilog. The selection between Moore and Mealy machines is determined by the precise necessities of the digital circuit and the design targets of the designer.

FSMs are a elementary idea in digital design, and understanding the variations between Moore and Mealy machines is essential for designing environment friendly and dependable digital circuits.

Finite State Machine Verilog Code Examples

Finite state machines are a elementary idea in digital electronics and are broadly utilized in varied functions. They are often carried out utilizing Verilog, a {hardware} description language (HDL) used for designing and verifying digital circuits. On this part, we are going to talk about varied examples of finite state machine implementations in Verilog.

Easy FSM

A easy FSM is a primary instance of a finite state machine that may be carried out in Verilog. It consists of a single state and a clock sign that toggles the state between 0 and 1. Here is an instance code for a easy FSM:

“`verilog

module simple_fsm (

enter clk,

output reg q

);

reg [1:0] state;

all the time @(posedge clk) start

case (state)

2’b00: state = 2’b01;

2’b01: state = 2’b10;

2’b10: state = 2’b11;

default: state = 2’b00;

endcase

finish

assign q = state[0];

endmodule

“`

This code defines a module known as `simple_fsm` that has a single enter `clk` and a single output `q`. The state is represented by a 2-bit register `state` and is toggled between 0 and 1 primarily based on the present worth of `state`. The `q` output is assigned the worth of the least important little bit of the `state` register.

FSM with Flags

A FSM with flags is a extra complicated instance that makes use of flags to implement a finite state machine. Flags are used to point sure situations or occasions that have to be dealt with by the FSM. On this instance, we are going to use two flags `flag1` and `flag2` to implement a FSM that toggles the state between 0 and 1 primarily based on the flag values.

“`verilog

module fsm_with_flags (

enter clk,

enter flag1,

enter flag2,

output reg q

);

reg [1:0] state;

all the time @(posedge clk) start

case (state)

2’b00: start

if (flag1) state = 2’b01;

else state = 2’b10;

finish

2’b01: start

if (flag2) state = 2’b10;

else state = 2’b11;

finish

2’b10: start

if (!flag1) state = 2’b11;

else state = 2’b00;

finish

default: state = 2’b00;

endcase

finish

assign q = state[0];

endmodule

“`

This code defines a module known as `fsm_with_flags` that has three inputs `clk`, `flag1`, and `flag2`, and a single output `q`. The state is represented by a 2-bit register `state` and is toggled between 0 and 1 primarily based on the present values of `flag1` and `flag2`. The `q` output is assigned the worth of the least important little bit of the `state` register.

Moore Machine, Finite state machine verilog

A Moore machine is a sort of finite state machine that’s used to implement digital circuits. It consists of a state register and a set of output indicators that depend upon the present state. Here is an instance code for a Moore machine:

“`verilog

module moore_machine (

enter clk,

output reg q

);

reg [1:0] state;

all the time @(posedge clk) start

case (state)

2’b00: state = 2’b01;

2’b01: state = 2’b10;

2’b10: state = 2’b11;

default: state = 2’b00;

endcase

finish

assign q = state[0];

endmodule

“`

This code defines a module known as `moore_machine` that has a single enter `clk` and a single output `q`. The state is represented by a 2-bit register `state` and is toggled between 0 and 1 primarily based on the present worth of `state`. The `q` output is assigned the worth of the least important little bit of the `state` register.

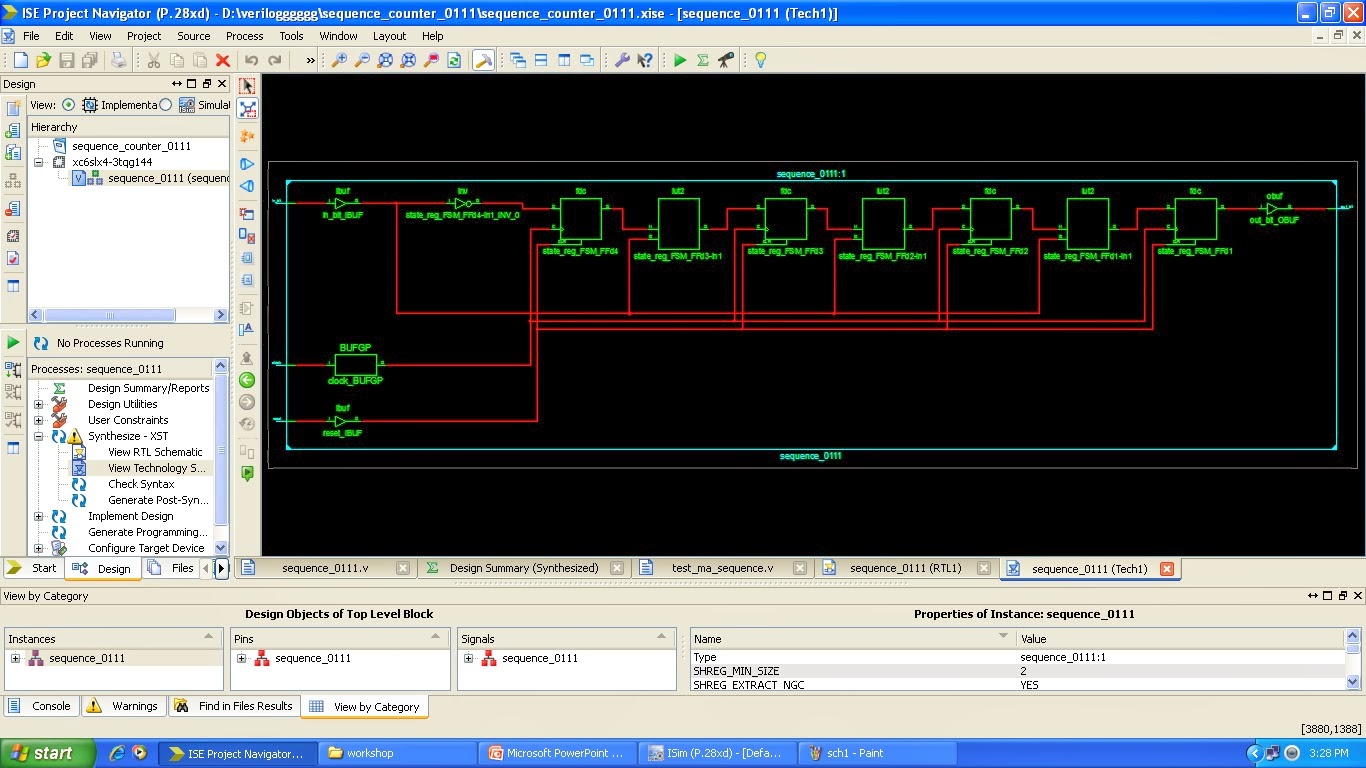

Finite State Machine Synthesis

![[GET ANSWER] Complete the Verilog HDL design for the following finite ... Finite state machine verilog](https://cdn.numerade.com/ask_images/fea93983002d495b8e6f81188f3a32cc.jpg)

Finite State Machine (FSM) synthesis is the method of reworking a high-level FSM design right into a low-level digital circuit that may be carried out on a programmable logic machine (PLD) or an application-specific built-in circuit (ASIC). The objective of FSM synthesis is to supply an optimized digital circuit that meets the specified efficiency and space necessities.

FSM Synthesis Course of

FSM synthesis sometimes includes a number of steps:

–

FSM Optimization

– This step includes optimizing the FSM design to scale back the variety of states and transitions, and to attenuate the world and energy consumption of the ensuing digital circuit.

– Strategies utilized in FSM optimization embody state minimization, transition optimization, and don’t-care state detection.

–

FSM Encoding

– This step includes encoding the optimized FSM design utilizing an acceptable encoding scheme, equivalent to binary encoding or grey encoding.

– The selection of encoding scheme is determined by the precise necessities of the digital circuit, together with the specified trade-offs between space, energy consumption, and efficiency.

–

Optimizing FSM Design for Space or Velocity

FSM design will be optimized for both space or pace, relying on the precise necessities of the digital circuit. Some widespread strategies for optimizing FSM design for space or pace embody:

- Totally Static FSM (FSFSM) synthesis: FSFSM synthesis is an optimization approach that mixes some great benefits of static FSM synthesis with the world effectivity of totally static logic.

- Semi-static FSM (SSFSM) synthesis: SSFSM synthesis is one other optimization approach that goals to scale back energy consumption and enhance space effectivity.

- Asynchronous FSM (AFSM) synthesis: AFSM synthesis is an optimization approach that goals to scale back energy consumption and enhance space effectivity, whereas minimizing the necessity for clock gating.

Case Research: FSM Synthesis for a Actual-World System

One widespread instance of a real-world system that may be carried out utilizing a FSM is a visitors gentle controller. A visitors gentle controller is an easy digital system that consists of a FSM that controls the timing of the visitors lights at an intersection. The FSM will be designed to optimize the timing of the visitors lights to attenuate congestion and cut back journey time.

FSM synthesis can be utilized to optimize the management algorithm of the visitors gentle controller to scale back vitality consumption, enhance visitors move, and improve security.

| Technique | Space | Energy Consumption | Velocity |

|---|---|---|---|

| FSFSM Synthesis | Low | Excessive | Excessive |

| SSFSM Synthesis | Medium | Medium | Medium |

| AFSM Synthesis | Excessive | Low | Low |

Conclusive Ideas

With the data and understanding of Finite State Machines in Verilog, now you can design and implement complicated programs and software program with ease. Whether or not you’re a newbie or an skilled engineer, this text has offered you with a complete overview of the idea of Finite State Machines in Verilog. Keep in mind, the important thing to mastering Finite State Machines in Verilog is to apply designing and implementing them, and to by no means cease studying and experimenting with new ideas and strategies.

Solutions to Frequent Questions: Finite State Machine Verilog

What’s a finite state machine?

A finite state machine is a mathematical mannequin that consists of a set of states, a set of inputs, and a set of outputs. It’s used to explain the conduct of a system or a tool by way of its inputs and outputs.

What’s the distinction between Mealy and Moore machines?

A Mealy machine produces an output primarily based on the present state and the enter, whereas a Moore machine produces an output primarily based on the present state solely. Mealy machines are extra versatile and can be utilized to implement extra complicated programs, whereas Moore machines are easier and extra environment friendly.

How do you design a Finite State Machine in Verilog?

To design a Finite State Machine in Verilog, you should determine the totally different states of the machine, the inputs and outputs, and the transition features between states. You possibly can then use the Verilog programming language to implement the machine’s conduct.

What’s the significance of testing and verification in Finite State Machine design?

Testing and verification are essential in Finite State Machine design as a result of they assist be sure that the machine behaves appropriately and meets the required specs. You need to use testbenches and assertions to confirm the machine’s conduct and catch any bugs or errors.